MA180023 Microchip Technology, MA180023 Datasheet - Page 411

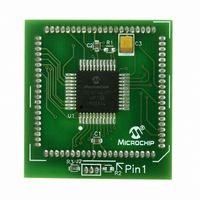

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 411 of 528

- Download datasheet (8Mb)

TABLE 26-2:

© 2009 Microchip Technology Inc.

BIT-ORIENTED OPERATIONS

BCF

BSF

BTFSC

BTFSS

BTG

CONTROL OPERATIONS

BC

BN

BNC

BNN

BNOV

BNZ

BOV

BRA

BZ

CALL

CLRWDT

DAW

GOTO

NOP

NOP

POP

PUSH

RCALL

RESET

RETFIE

RETLW

RETURN

SLEEP

Note 1:

Mnemonic,

Operands

2:

3:

4:

When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value

present on the pins themselves. For example, if the data latch is ‘1’ for a pin configured as input and is driven low by an

external device, the data will be written back with a ‘0’.

If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if

assigned.

If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second

cycle is executed as a NOP.

Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the

first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory

locations have a valid instruction.

f, b, a

f, b, a

f, b, a

f, b, a

f, b, a

n

n

n

n

n

n

n

n

n

n, s

—

—

n

—

—

—

—

n

s

k

s

—

PIC18F46J11 FAMILY INSTRUCTION SET (CONTINUED)

Bit Clear f

Bit Set f

Bit Test f, Skip if Clear

Bit Test f, Skip if Set

Bit Toggle f

Branch if Carry

Branch if Negative

Branch if Not Carry

Branch if Not Negative

Branch if Not Overflow

Branch if Not Zero

Branch if Overflow

Branch Unconditionally

Branch if Zero

Call Subroutine

Clear Watchdog Timer

Decimal Adjust WREG

Go to Address

No Operation

No Operation

Pop Top of Return Stack (TOS)

Push Top of Return Stack (TOS)

Relative Call

Software Device Reset

Return from Interrupt Enable

Return with Literal in WREG

Return from Subroutine

Go into Standby mode

Description

1st word

2nd word

1st word

2nd word

1

1

1 (2 or 3)

1 (2 or 3)

1

1 (2)

1 (2)

1 (2)

1 (2)

1 (2)

1 (2)

1 (2)

2

1 (2)

2

1

1

2

1

1

1

1

2

1

2

2

2

1

Cycles

PIC18F46J11 FAMILY

1001

1000

1011

1010

0111

1110

1110

1110

1110

1110

1110

1110

1101

1110

1110

1111

0000

0000

1110

1111

0000

1111

0000

0000

1101

0000

0000

0000

0000

0000

MSb

16-Bit Instruction Word

bbba

bbba

bbba

bbba

bbba

0010

0110

0011

0111

0101

0001

0100

0nnn

0000

110s

kkkk

0000

0000

1111

kkkk

0000

xxxx

0000

0000

1nnn

0000

0000

1100

0000

0000

ffff

ffff

ffff

ffff

ffff

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

kkkk

kkkk

0000

0000

kkkk

kkkk

0000

xxxx

0000

0000

nnnn

1111

0001

kkkk

0001

0000

ffff

ffff

ffff

ffff

ffff

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

nnnn

kkkk

kkkk

0100

0111

kkkk

kkkk

0000

xxxx

0110

0101

nnnn

1111

000s

kkkk

001s

0011

LSb

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

TO, PD

C

None

None

None

None

None

None

All

GIE/GIEH,

PEIE/GIEL

None

None

TO, PD

Affected

Status

DS39932C-page 411

1, 2

1, 2

3, 4

3, 4

1, 2

4

Notes

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: