MA180023 Microchip Technology, MA180023 Datasheet - Page 45

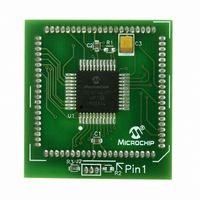

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 45 of 528

- Download datasheet (8Mb)

3.3

The power-managed Sleep mode is identical to the

legacy Sleep mode offered in all other PIC devices. It is

entered by clearing the IDLEN bit (the default state on

device Reset) and executing the SLEEP instruction.

This shuts down the selected oscillator (Figure 3-5). All

clock source status bits are cleared.

Entering the Sleep mode from any other mode does not

require a clock switch. This is because no clocks are

needed once the controller has entered Sleep mode. If

the WDT is selected, the INTRC source will continue to

operate. If the Timer1 oscillator is enabled, it will also

continue to run.

FIGURE 3-5:

FIGURE 3-6:

© 2009 Microchip Technology Inc.

Peripheral

Program

Counter

OSC1

Sleep

Clock

Clock

CPU

Note 1: T

CPU Clock

PLL Clock

Peripheral

Program

Sleep Mode

Counter

Output

OSC1

Clock

Q1

Q2

OST

PC

Q3

= 1024 T

Wake Event

Q4

TRANSITION TIMING FOR ENTRY TO SLEEP MODE

TRANSITION TIMING FOR WAKE FROM SLEEP (HSPLL)

Q1

Q1

OSC

T

OST

; T

PLL

(1)

= 2 ms (approx). These intervals are not shown to scale.

PC

T

PLL

OSTS Bit Set

(1)

Q2 Q3 Q4 Q1 Q2

PC + 2

PIC18F46J11 FAMILY

When a wake event occurs in Sleep mode (by interrupt,

Reset or WDT time-out), the device will not be clocked

until the clock source selected by the SCS<1:0> bits

becomes ready (see Figure 3-6), or it will be clocked

from the internal oscillator if either the Two-Speed

Start-up or the FSCM is enabled (see Section 25.0

“Special Features of the CPU”). In either case, the

OSTS bit is set when the primary clock is providing the

device clocks. The IDLEN and SCS bits are not

affected by the wake-up.

PC + 2

Q3 Q4 Q1 Q2

PC + 4

Q3 Q4

Q1 Q2 Q3 Q4

PC + 6

DS39932C-page 45

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: