MA180023 Microchip Technology, MA180023 Datasheet - Page 430

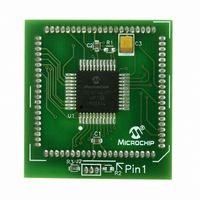

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 430 of 528

- Download datasheet (8Mb)

PIC18F46J11 FAMILY

IORLW

Syntax:

Operands:

Operation:

Status Affected:

Encoding:

Description:

Words:

Cycles:

Example:

DS39932C-page 430

Q Cycle Activity:

Before Instruction

After Instruction

Decode

W

W

Q1

=

=

Inclusive OR Literal with W

IORLW k

0 ≤ k ≤ 255

(W) .OR. k → W

N, Z

The contents of W are ORed with the

eight-bit literal ‘k’. The result is placed

in W.

1

1

literal ‘k’

IORLW

Read

0000

Q2

9Ah

BFh

1001

35h

Process

Data

Q3

kkkk

Write to

Q4

W

kkkk

IORWF

Syntax:

Operands:

Operation:

Status Affected:

Encoding:

Description:

Words:

Cycles:

Example:

Q Cycle Activity:

Before Instruction

After Instruction

Decode

RESULT =

W

RESULT =

W

Q1

=

=

register ‘f’

Inclusive OR W with f

IORWF

0 ≤ f ≤ 255

d ∈ [0,1]

a ∈ [0,1]

(W) .OR. (f) → dest

N, Z

Inclusive OR W with register ‘f’. If ‘d’ is

‘0’, the result is placed in W. If ‘d’ is ‘1’,

the result is placed back in register ‘f’

(default).

If ‘a’ is ‘0’, the Access Bank is selected.

If ‘a’ is ‘1’, the BSR is used to select the

GPR bank (default).

If ‘a’ is ‘0’ and the extended instruction

set is enabled, this instruction operates

in Indexed Literal Offset Addressing

mode whenever f ≤ 95 (5Fh). See

Section 26.2.3 “Byte-Oriented and

Bit-Oriented Instructions in Indexed

Literal Offset Mode” for details.

1

1

IORWF

Read

0001

Q2

13h

91h

13h

93h

© 2009 Microchip Technology Inc.

RESULT, 0, 1

f {,d {,a}}

00da

Process

Data

Q3

ffff

destination

Write to

Q4

ffff

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: