UPD78F0078GK-9ET-A Renesas Electronics America, UPD78F0078GK-9ET-A Datasheet - Page 296

UPD78F0078GK-9ET-A

Manufacturer Part Number

UPD78F0078GK-9ET-A

Description

Manufacturer

Renesas Electronics America

Datasheet

1.UPD78F0078GK-9ET-A.pdf

(598 pages)

Specifications of UPD78F0078GK-9ET-A

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 296 of 598

- Download datasheet (4Mb)

CHAPTER 15 SERIAL INTERFACE UART2

(d) Reception

The interface enters the reception wait status if the UART transfer mode is specified by using transfer mode

specification register 2 (TRMC2) and bit 5 (RXE2) of asynchronous serial interface mode register 2 (ASIM2)

is set to 1 after bit 7 (POWER2) has been set to 1. In this status, the R

D2 pin is monitored to detect the

X

start bit. When the start bit is detected, reception is started, and serial data is sequentially stored in receive

shift register 2 (RX2) at the specified baud rate.

When the stop bit is received, a receive completion interrupt (INTSR2) occurs and, at the same time, the

data in RX2 is written to receive buffer register 2 (RXB2). If an overrun error (OVE2) occurs, however, the

receive data is not written to RXB2 but discarded. Even if a parity error (PE2) or framing error (FE2) occurs

during reception, reception continues up to the position at which the stop bit is received, and an error interrupt

(INTSR2/INTSER2) occurs after completion of reception.

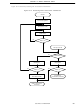

Figure 15-17. Timing of Asynchronous Serial Interface Receive Completion Interrupt Request

RxD2 (input)

Start

D0

D1

D2

D6

D7

Parity

Stop

INTSR2

RXB2

Caution

During reception, the number of stop bits is always 1. A second stop bit is ignored.

294

User’s Manual U14260EJ4V0UD

Related parts for UPD78F0078GK-9ET-A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: