UPD78F0078GK-9ET-A Renesas Electronics America, UPD78F0078GK-9ET-A Datasheet - Page 299

UPD78F0078GK-9ET-A

Manufacturer Part Number

UPD78F0078GK-9ET-A

Description

Manufacturer

Renesas Electronics America

Datasheet

1.UPD78F0078GK-9ET-A.pdf

(598 pages)

Specifications of UPD78F0078GK-9ET-A

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 299 of 598

- Download datasheet (4Mb)

15.4.3 Multi-processor transfer mode

(1) Registers to be used

Note

Caution When using UART2, stop the operation of SIO3 (bit 7 (CSIE3) of serial operation mode register 3

Remark

POW TXE2 RXE2 PS21 PS20

ER2

1

1

1

In this mode, data can be transferred to or received from two or more processors.

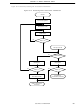

<1> Set the CKSEL2 register (see Figure 15-7).

<2> Set the BRGC2 register (see Figure 15-6).

<3> Set bits 7 and 6 (TRM12 and TRM02) of the TRMC2 register to 0 and 1, and set bits 3, 1, and 0 (ISMD2,

<4> Set bits 4 to 0 (PS21, PS20, CL2, SL2, and ISEM2) of the ASIM2 register (see Figure 15-3).

<5> Set bit 7 (POWER2) of the ASIM2 register to 1.

<6> Set bit 6 (TXE2) of the ASIM2 register to 1.

<7> Set bit 5 (RXE2) of the ASIM2 register to 1.

<8> Write data to TXB2.

Caution Take relationship with the other party of communication when setting the port mode register

The basic procedure of setting an operation in the multi-processor transfer mode is as follows.

The relationship between the register settings and pins is shown below.

Table 15-10. Relationship Between Register Settings and Pins (Multi-Processor Transfer Mode)

• Asynchronous serial interface mode register 2 (ASIM2)

• Asynchronous serial interface status register 2 (ASIS2)

• Baud rate generator control register 2 (BRGC2)

• Asynchronous serial interface transmit status register 2 (ASIF2)

• Clock select register 2 (CKSEL2)

• Transfer mode specification register 2 (TRMC2)

• Port mode register 3 (PM3)

• Port register 3 (P3)

Can be set as port function.

0

1

1

MPIEN2, and MPS2) (see Figure 15-8).

(CSIM3) = 0).

TRMC2: Transfer mode specification register 2, PM

P

: don’t care, ASIM2: Asynchronous serial interface mode register 2,

1

0

1

: Port output latch

and port register.

0/1

0/1

0/1

ASIM2

0/1

0/1

0/1

CL2

0/1

0/1

0/1

Data transmission is started.

SL2 ISEM2 TRM12 TRM02 ISMD2 MPIEN2 MPS2

0/1

0/1

CHAPTER 15 SERIAL INTERFACE UART2

0/1

0/1

User’s Manual U14260EJ4V0UD

0

0

0

1

1

1

TRMC2

0/1

0/1

Transmission is enabled.

Reception is enabled.

0/1

0/1

0/1

: Port mode register,

0/1

0/1

0/1

PM34 P34 PM35 P35 Operation Pin Function

Note

0

0

Note

0

0

Note

1

1

Note

Reception P34

Transmission/ TxD2

Transmission TxD2

reception

Mode

TxD2

P34/

SI3/

RxD2

RxD2

RxD2

SO3/

P35/

P35

297

Related parts for UPD78F0078GK-9ET-A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: