C8051F930-TB Silicon Laboratories Inc, C8051F930-TB Datasheet - Page 231

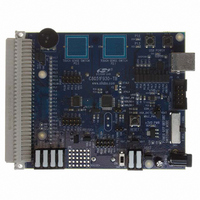

C8051F930-TB

Manufacturer Part Number

C8051F930-TB

Description

BOARD TARGET/PROTO W/C8051F930

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F930-TB

Contents

Board

Processor To Be Evaluated

C8051F930

Processor Series

C8051F9xx

Data Bus Width

8 bit

Interface Type

I2C, UART, SPI

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

0.9 V to 3.6 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

C8051F930

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1472

- Current page: 231 of 324

- Download datasheet (3Mb)

SFR Definition 21.19. P2SKIP: Port2 Skip

SFR Page = 0x0; SFR Address = 0xD6

SFR Definition 21.20. P2MDIN: Port2 Input Mode

SFR Page = 0x0; SFR Address = 0xF3

Note: Pins P2.0-P2.6 are only available in 32-pin devices.

Note: Pins P2.0-P2.6 are only available in 32-pin devices.

Reset

Reset

Name

Name Reserved

Type

7:0

Type

Bit

6:0

Bit

Bit

Bit

7

P2SKIP[7:0]

P2MDIN[3:0] Analog Configuration Bits for P2.6–P2.0 (respectively).

Name

Name

7

0

7

1

Port 1 Crossbar Skip Enable Bits.

These bits select Port 2 pins to be skipped by the Crossbar Decoder. Port pins

used for analog, special functions or GPIO should be skipped by the Crossbar.

0: Corresponding P2.n pin is not skipped by the Crossbar.

1: Corresponding P2.n pin is skipped by the Crossbar.

Reserved. Read = 1b; Must Write 1b.

Port pins configured for analog mode have their weak pullup and digital receiver

disabled. The digital driver is not explicitly disabled.

0: Corresponding P2.n pin is configured for analog mode.

1: Corresponding P2.n pin is not configured for analog mode.

0

1

6

6

Description

5

0

5

1

Rev. 1.1

4

0

4

1

P2SKIP[7:0]

R/W

R/W

P2MDIN[6:0]

C8051F93x-C8051F92x

Function

Read

3

0

3

1

2

0

2

1

1

0

1

1

Write

0

0

0

1

231

Related parts for C8051F930-TB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc