C8051F930-TB Silicon Laboratories Inc, C8051F930-TB Datasheet - Page 70

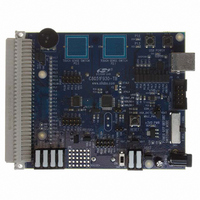

C8051F930-TB

Manufacturer Part Number

C8051F930-TB

Description

BOARD TARGET/PROTO W/C8051F930

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F930-TB

Contents

Board

Processor To Be Evaluated

C8051F930

Processor Series

C8051F9xx

Data Bus Width

8 bit

Interface Type

I2C, UART, SPI

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

0.9 V to 3.6 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

C8051F930

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1472

- Current page: 70 of 324

- Download datasheet (3Mb)

C8051F93x-C8051F92x

5.2.4. Settling Time Requirements

A minimum amount of tracking time is required before each conversion can be performed, to allow the

sampling capacitor voltage to settle. This tracking time is determined by the AMUX0 resistance, the ADC0

sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note

that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion.

For many applications, these three SAR clocks will meet the minimum tracking time requirements, and

higher values for the external source impedance will increase the required tracking time.

Figure 5.4 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling

accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or

V

ments as well as the mux impedance and sampling capacitor values.

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB)

t is the required settling time in seconds

R

n is the ADC resolution in bits (10).

70

DD

TOTAL

with respect to GND, R

is the sum of the AMUX0 resistance and any external source resistance.

Note: The value of CSAMPLE depends on the PGA Gain. See Table 4.9 for details.

Equation 5.1. ADC0 Settling Time Requirements

Figure 5.4. ADC0 Equivalent Input Circuits

TOTAL

P0.x

t

reduces to R

=

RC

ln

MUX Select

Input

------ -

SA

2

= R

n

MUX

MUX

Rev. 1.1

R

* C

. See Table 4.9 for ADC0 minimum settling time require-

TOTAL

R

MUX

SAMPLE

C

SAMPLE

C

SAMPLE

Related parts for C8051F930-TB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc