C8051F930-TB Silicon Laboratories Inc, C8051F930-TB Datasheet - Page 237

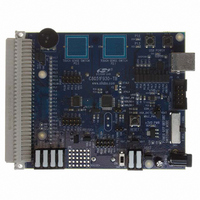

C8051F930-TB

Manufacturer Part Number

C8051F930-TB

Description

BOARD TARGET/PROTO W/C8051F930

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F930-TB

Contents

Board

Processor To Be Evaluated

C8051F930

Processor Series

C8051F9xx

Data Bus Width

8 bit

Interface Type

I2C, UART, SPI

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

0.9 V to 3.6 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

C8051F930

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1472

- Current page: 237 of 324

- Download datasheet (3Mb)

22.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting con-

trol for serial transfers; higher level protocol is determined by user software. The SMBus interface provides

the following application-independent features:

•

•

•

•

•

•

•

•

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware

acknowledgement is disabled, the point at which the interrupt is generated depends on whether the

hardware is acting as a data transmitter or receiver. When a transmitter (i.e., sending address/data,

receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received

ACK value; when receiving data (i.e., receiving address/data, sending an ACK), this interrupt is generated

before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement

is enabled, these interrupts are always generated after the ACK cycle. See Section 22.5 for more details

on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or

the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control

register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 22.4.2;

Table 22.5 provides a quick SMB0CN decoding reference.

Byte-wise serial data transfers

Clock signal generation on SCL (Master Mode only) and SDA data synchronization

Timeout/bus error recognition, as defined by the SMB0CF configuration register

START/STOP timing, detection, and generation

Bus arbitration

Interrupt generation

Status information

Optional hardware recognition of slave address and automatic acknowledgement of address/data

Rev. 1.1

C8051F93x-C8051F92x

237

Related parts for C8051F930-TB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc