DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 171

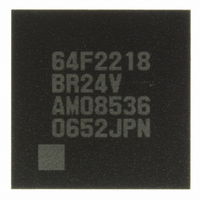

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 171 of 758

- Download datasheet (5Mb)

This LSI has a built-in bus controller (BSC) that manages the external address space divided into

eight areas. The bus controller also has a bus arbitration function, and controls the operation of the

internal bus masters: the CPU and DMA controller (DMAC).

6.1

• Manages external address space in area units

• Basic bus interface*

• Burst ROM interface*

• Idle cycle insertion*

• Bus arbitration

• Other features

Notes: 1. Chip select CS6 in area 6 is for the on-chip USB. Therefore it cannot be used as an

BSCS207A_010020020100

⎯ Manages the external space as 8 areas of 2-Mbytes

⎯ Bus specifications can be set independently for each area

⎯ Burst ROM interface can be set

⎯ Chip select (CS0 to CS5) can be output for areas 0 to 5*

⎯ 8-bit access or 16-bit access can be selected for each area

⎯ 2-state access or 3-state access can be selected for each area

⎯ Program wait states can be inserted for each area

⎯ Burst ROM interface can be selected for area 0

⎯ One or two states can be selected for the burst cycle

⎯ Idle cycle can be inserted between consecutive read accesses to different areas

⎯ Idle cycle can be inserted before a write access to an external area immediately after a read

⎯ The on-chip bus arbiter arbitrates bus mastership among CPU and DMAC

⎯ External bus release function*

access to an external area

2. These functions are not available in the H8S/2212 Group.

Features

external area. 8-bit bus mode, 3-state access, and no program wait state should be set

for area 6. Access to the RTC related registers (address: H'FFFF40 to H'FFFF5F)

follows the specification of area 7. 8-bit access, 3-state access, and no program wait

state should be set for area 7.

1

2

2

Section 6 Bus Controller

2

Rev.7.00 Dec. 24, 2008 Page 115 of 698

2

REJ09B0074-0700

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: