DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 471

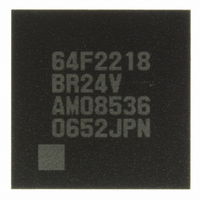

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 471 of 758

- Download datasheet (5Mb)

12.5.1

Figure 12.14 shows a sample flowchart for multiprocessor serial data transmission. For an ID

transmission cycle, set the MPBT bit in SSR to 1 before transmission. For a data transmission

cycle, clear the MPBT bit in SSR to 0 before transmission. All other SCI operations are the same

as those in asynchronous mode.

Figure 12.14 Sample Multiprocessor Serial Data Transmission Flowchart

Multiprocessor Serial Data Transmission

Clear DR to 0 and set DDR to 1

Write transmit data to TDR and

Read TDRE flag in SSR

Read TEND flag in SSR

Clear TE bit in SCR to 0

set MPBT bit in SSR

Clear TDRE flag to 0

All data transmitted?

Start transmission

Break output?

Initialization

TDRE = 1

TEND = 1

<End>

Yes

Yes

Yes

Yes

No

No

No

No

[1]

[2]

[3]

[4]

[1]

[2]

[3]

[4]

Rev.7.00 Dec. 24, 2008 Page 415 of 698

SCI initialization:

The TxD pin is automatically

designated as the transmit data

output pin.

After the TE bit is set to 1, a frame of

1s is output, and transmission is

enabled.

SCI status check and transmit data

write:

Read SSR and check that the TDRE

flag is set to 1, then write transmit

data to TDR. Set the MPBT bit in

SSR to 0 or 1. Finally, clear the

TDRE flag to 0.

Serial transmission continuation

procedure:

To continue serial transmission, be

sure to read 1 from the TDRE flag to

confirm that writing is possible, then

write data to TDR, and then clear the

TDRE flag to 0. Checking and

clearing of the TDRE flag is automatic

when the DMAC is activated by a

transmit data empty interrupt (TXI)

request, and data is written to TDR.

Break output at the end of serial

transmission:

To output a break in serial

transmission, set the port DDR to 1,

clear DR to 0, then clear the TE bit in

SCR to 0.

REJ09B0074-0700

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: