M306N4FGGP#U3 Renesas Electronics America, M306N4FGGP#U3 Datasheet - Page 209

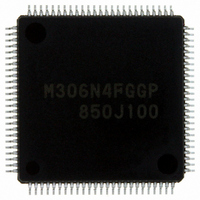

M306N4FGGP#U3

Manufacturer Part Number

M306N4FGGP#U3

Description

IC M16C/6N4 MCU FLASH 100-LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/6Nr

Specifications of M306N4FGGP#U3

Core Processor

M16C/60

Core Size

16-Bit

Speed

24MHz

Connectivity

CAN, I²C, IEBus, SIO, UART/USART

Peripherals

DMA, WDT

Number Of I /o

85

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

10K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 26x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LQFP

Package

100LQFP

Family Name

M16C

Maximum Speed

24 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16|32 Bit

Number Of Programmable I/os

87

Interface Type

I2C/UART

On-chip Adc

26-chx10-bit

On-chip Dac

2-chx8-bit

Number Of Timers

11

For Use With

R0K3306NKS001BE - KIT DEV RSK RSK-M16C/6NKR0K3306NKS000BE - KIT DEV RSK RSK-M16C/6NK

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 209 of 414

- Download datasheet (3Mb)

M16C/6N Group (M16C/6N4)

Rev.2.40

REJ09B0009-0240

Figure 15.32 Transmit and Receive Timing in SIM Mode

(1) Transmit timing

(2) Receive timing

Transfer clock

TE bit in U2C1

register

TI bit in U2C1

register

TXD2

Parity Error signal

returned from

Receiving end

RXD2

TXEPT bit in U2C0

register

IR bit in S2TIC

register

The above timing diagram applies to the case where data is

transmitted in the direct format.

The above timing diagram applies to the case where data is

received in the direct format.

NOTES:

Transfer clock

RE bit in U2C1

register

Transmit waveform

from the

Transmitting end

TXD2

RXD2 pin level

RI bit in U2C0

register

IR bit in S2RIC

register

STPS bit in U2MR register = 0 (1 stop bit)

PRY bit in U2MR register = 1 (even)

UFORM bit in U2C0 register = 0 (LSB first)

U2LCH bit in U2C1 register = 0 (no reverse)

U2IRS bit in U2C1 register = 1 (transmission completed)

STPS bit in U2MR register = 0 (1 stop bit)

PRY bit in U2MR register = 1 (even)

UFORM bit in U2C0 register = 0 (LSB first)

U2LCH bit In U2C1 register = 0 (no reverse)

U2IRS bit in U2C1 register = 1 (transmission completed)

1. Data transmission starts when BRG overflows after a value is set to the U2TB register on the rising edge of the TI bit.

2. Because the TXD2 and RXD2 pins are connected, a composite waveform, consisting of transmit waveform from the TXD2 pin and

3. Because the TXD2 and RxD2 pins are connected, a composite waveform, consisting of transmit waveform from the transmitting end

Apr 14, 2006

parity error signal from the receiving end, is generated.

and parity error signal from the TXD2 pin, is generated.

pin level

(2)

(3)

1

0

1

0

1

0

1

0

1

0

1

0

1

0

page 185 of 376

Start

ST

ST

Start

ST

ST

bit

bit

D0

D0

D0

D0

D1

D1

D1

D1

TC

TC

D2 D3

D2 D3

D2

D2

Data is written to the U2TB register

D3

D3

D4

D4

D4

D4

D5

D5

D5

D5

D6

D6

D6

D6

D7

D7

D7

D7

Parity

Parity

bit

bit

P

P

P

P

SP

SP

SP

SP

Set to 0 by an interrupt request acknowledgement or by program

Set to 0 by an interrupt request acknowledgement or by program

Stop

Stop

bit

bit

TC = 16(n+1) / fi or 16(n+1) / fEXT

TC = 16(n+1) / fi or 16(n+1) / fEXT

fi: frequency of U2BRG count source

fEXT: frequency of U2BRG count source (external clock)

n: value set to the U2BRG register

fi: frequency of U2BRG count source

fEXT: frequency of U2BRG count source (external clock)

n: value set to the U2BRG register

(f1SIO, f2SIO, f8SIO, f32SIO)

(f1SIO, f2SIO, f8SIO, f32SIO)

ST

ST

ST

ST

An interrupt routine

detects "H" or "L"

Data is transferred from the U2TB

register to the UART2 transmit register

(NOTE 1)

An "L" signal is applied from the

SIM card due to a parity error

D0

D0

D0

D0

Read the U2RB register

D1

D1

D1

D1

TXD2 provides "L" output

due to a parity error

D2

D2

D2

D2

An interrupt routine detects "H" or "L"

D3

D3

D3

D3

D4

D4

D4

D4

D5

D5

D5

D5

D6

D6

D6

D6

D7

D7

D7

D7

15. Serial Interface

P

P

P

P

SP

SP

SP

SP

Related parts for M306N4FGGP#U3

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: