M306N4FGGP#U3 Renesas Electronics America, M306N4FGGP#U3 Datasheet - Page 71

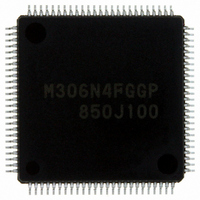

M306N4FGGP#U3

Manufacturer Part Number

M306N4FGGP#U3

Description

IC M16C/6N4 MCU FLASH 100-LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/6Nr

Specifications of M306N4FGGP#U3

Core Processor

M16C/60

Core Size

16-Bit

Speed

24MHz

Connectivity

CAN, I²C, IEBus, SIO, UART/USART

Peripherals

DMA, WDT

Number Of I /o

85

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

10K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 26x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LQFP

Package

100LQFP

Family Name

M16C

Maximum Speed

24 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16|32 Bit

Number Of Programmable I/os

87

Interface Type

I2C/UART

On-chip Adc

26-chx10-bit

On-chip Dac

2-chx8-bit

Number Of Timers

11

For Use With

R0K3306NKS001BE - KIT DEV RSK RSK-M16C/6NKR0K3306NKS000BE - KIT DEV RSK RSK-M16C/6NK

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 71 of 414

- Download datasheet (3Mb)

M16C/6N Group (M16C/6N4)

Rev.2.40

REJ09B0009-0240

Table 7.7 External Bus Status When Internal Area Accessed

Figure 7.6 CSE Register

________

7.2.9 External Bus Status when Internal Area Accessed

A0 to A19

D0 to D15 When read High-impedance

_____

RD, WR, WRL, WRH

BHE

_______

CS0 to CS3

ALE

7.2.10 Software Wait

Table 7.7 shows the External Bus Status When Internal Area Accessed.

Software wait states can be inserted by using the PM17 bit in the PM1 register, bits CS0W to CS3W in the

CSR register, and the CSE register. The SFR area is unaffected by these control bits. This area is always

accessed in 2 BCLK or 3 BCLK cycles as determined by the PM20 bit in the PM2 register. See Table 7.8

Bit and Bus Cycle Related to Software Wait for details.

To use the RDY signal, set the corresponding bit of bits CS3W to CS0W to 0 (with wait state).

Figure 7.6 shows the CSE Register. Table 7.8 shows the Software Wait Related Bits and Bus Cycles.

Figures 7.7 and 7.8 show the Typical Bus Timings Using Software Wait.

Chip Select Expansion Control Register

NOTE:

______

b7

Apr 14, 2006

1. Set the CSiW bit (i = 0 to 3) in the CSR register to 0 (with wait state) before writing to bits CSEi1W to CSEi0W.

_______

b6

If the CSiW bit needs to be set to 1 (without wait state), set bits CSEi1W to CSEi0W to 00b before setting it.

Item

________

b5

When write Output data

________

b4

_________

b3

page 47 of 376

b2

b1

________

Address output

RD, WR, WRL, WRH output

BHE output

Output “H”

Output “L”

_____

b0

Bit Symbol

______

CSE00W

CSE01W

CSE10W

CSE11W

CS20WE

CSE21W

CSE30W

CSE31W

Symbol

CSE

SFR Accessed

_________ __________

CS0 wait expansion bits

CS1 wait expansion bits

CS2 wait expansion bits

CS3 wait expansion bits

Address

001Bh

Bit Name

Maintain status before accessed address

of external area or SFR

High-impedance

Undefined

Output “H”

Maintain status before accessed status of

external area or SFR

Output “H”

Output “L”

(1)

(1)

(1)

(1)

After Reset

Internal ROM, Internal RAM Accessed

00h

b1 b0

b3 b2

b5 b4

b7 b6

0 0 : 1 wait

0 1 : 2 waits

1 0 : 3 waits

1 1 : Do not set a value

0 0 : 1 wait

0 1 : 2 waits

1 0 : 3 waits

1 1 : Do not set a value

0 0 : 1 wait

0 1 : 2 waits

1 0 : 3 waits

1 1 : Do not set a value

0 0 : 1 wait

0 1 : 2 waits

1 0 : 3 waits

1 1 : Do not set a value

Function

RW

RW

RW

RW

RW

RW

RW

RW

RW

7. Bus

Related parts for M306N4FGGP#U3

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: