mc9s12xd256 Freescale Semiconductor, Inc, mc9s12xd256 Datasheet - Page 72

mc9s12xd256

Manufacturer Part Number

mc9s12xd256

Description

Hcs12x Microcontrollers

Manufacturer

Freescale Semiconductor, Inc

Datasheet

1.MC9S12XD256.pdf

(1350 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

mc9s12xd256CAA

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

mc9s12xd256CAG

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 72 of 1350

- Download datasheet (8Mb)

Chapter 1 Device Overview MC9S12XD-Family

1.5.2.1

The system stop modes are entered if the CPU executes the STOP instruction and the XGATE doesn’t

execute a thread and the XGFACT bit in the XGMCTL register is cleared. Depending on the state of the

PSTP bit in the CLKSEL register the MCU goes into pseudo stop mode or full stop mode. Please refer to

CRG section. Asserting RESET, XIRQ, IRQ or any other interrupt ends the system stop modes.

1.5.2.2

In this mode the clocks are stopped but the oscillator is still running and the real time interrupt (RTI) or

watchdog (COP) submodule can stay active. Other peripherals are turned off. This mode consumes more

current than the system stop mode, but the wake up time from this mode is significantly shorter.

1.5.2.3

The oscillator is stopped in this mode. All clocks are switched off. All counters and dividers remain frozen.

1.5.2.4

This mode is entered when the CPU executes the WAI instruction. In this mode the CPU will not execute

instructions. The internal CPU clock is switched off. All peripherals and the XGATE can be active in

system wait mode. For further power consumption the peripherals can individually turn off their local

clocks. Asserting RESET, XIRQ, IRQ or any other interrupt that has not been masked ends system wait

mode.

1.5.3

The enhanced capture timer, pulse width modulator, analog-to-digital converters, the periodic interrupt

timer and the XGATE module provide a software programmable option to freeze the module status during

the background debug module is active. This is useful when debugging application software. For detailed

description of the behavior of the ATD0, ATD1, ECT, PWM, XGATE and PIT when the background debug

module is active consult the corresponding sections..

1.6

Consult the S12XCPU Block Guide for information on exception processing.

1.6.1

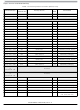

Table 1-12

(S12XINT) provides an interrupt vector base register (IVBR) to relocate the vectors. Associated with each

I-bit maskable service request is a configuration register. It selects if the service request is enabled, the

service request priority level and whether the service request is handled either by the S12X CPU or by the

XGATE module.

72

Resets and Interrupts

lists all interrupt sources and vectors in the default order of priority. The interrupt module

Freeze Mode

Vectors

System Stop Modes

Pseudo Stop Mode

Full Stop Mode

System Wait Mode

MC9S12XDP512 Data Sheet, Rev. 2.17

Freescale Semiconductor

Related parts for mc9s12xd256

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: