mc9s12xd256 Freescale Semiconductor, Inc, mc9s12xd256 Datasheet - Page 95

mc9s12xd256

Manufacturer Part Number

mc9s12xd256

Description

Hcs12x Microcontrollers

Manufacturer

Freescale Semiconductor, Inc

Datasheet

1.MC9S12XD256.pdf

(1350 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

mc9s12xd256CAA

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

mc9s12xd256CAG

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 95 of 1350

- Download datasheet (8Mb)

Freescale Semiconductor

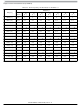

WRTMASK

CR[1:0]

Field

2–0

5

Write Mask for WCOP and CR[2:0] Bit — This write-only bit serves as a mask for the WCOP and CR[2:0] bits

while writing the COPCTL register. It is intended for BDM writing the RSBCK without touching the contents of

WCOP and CR[2:0].

0 Write of WCOP and CR[2:0] has an effect with this write of COPCTL

1 Write of WCOP and CR[2:0] has no effect with this write of COPCTL. (Does not count for “write once”.)

COP Watchdog Timer Rate Select — These bits select the COP time-out rate (see

time-out period is OSCCLK period divided by CR[2:0] value. Writing a nonzero value to CR[2:0] enables the

COP counter and starts the time-out period. A COP counter time-out causes a system reset. This can be

avoided by periodically (before time-out) reinitializing the COP counter via the ARMCOP register.

While all of the following four conditions are true the CR[2:0], WCOP bits are ignored and the COP operates at

highest time-out period (

1) COP is enabled (CR[2:0] is not 000)

2) BDM mode active

3) RSBCK = 0

4) Operation in emulation or special modes

1

OSCCLK cycles are referenced from the previous COP time-out reset

(writing 0x_55/0x_AA to the ARMCOP register)

CR2

Table 2-9. COPCTL Field Descriptions (continued)

0

0

0

0

1

1

1

1

2

24

MC9S12XDP512 Data Sheet, Rev. 2.17

Table 2-10. COP Watchdog Rates

cycles) in normal COP mode (Window COP mode disabled):

CR1

0

0

1

1

0

0

1

1

CR0

0

1

0

1

0

1

0

1

Description

Cycles to Time-out

Chapter 2 Clocks and Reset Generator (S12CRGV6)

COP disabled

OSCCLK

1

2

2

2

2

2

2

2

14

16

18

20

22

23

24

Table

2-10). The COP

95

Related parts for mc9s12xd256

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: