MC9S12XEP100CAL Freescale Semiconductor, MC9S12XEP100CAL Datasheet - Page 774

MC9S12XEP100CAL

Manufacturer Part Number

MC9S12XEP100CAL

Description

IC MCU 16BIT 1M FLASH 112-LQFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Datasheet

1.MC9S12XEP768CAL.pdf

(1328 pages)

Specifications of MC9S12XEP100CAL

Core Processor

HCS12X

Core Size

16-Bit

Speed

50MHz

Connectivity

CAN, EBI/EMI, I²C, IrDA, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

91

Program Memory Size

1MB (1M x 8)

Program Memory Type

FLASH

Eeprom Size

4K x 8

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

1.72 V ~ 5.5 V

Data Converters

A/D 16x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

112-LQFP

Processor Series

S12XE

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

64 KB

Interface Type

CAN/SCI/SPI

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

91

Number Of Timers

25

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

KIT33812ECUEVME, EVB9S12XEP100, DEMO9S12XEP100

Minimum Operating Temperature

- 40 C

On-chip Adc

16-ch x 12-bit

Package

112LQFP

Family Name

HCS12X

Maximum Speed

50 MHz

Operating Supply Voltage

1.8|2.8|5 V

For Use With

EVB9S12XEP100 - BOARD EVAL FOR MC9S12XEP100DEMO9S12XEP100 - BOARD DEMO FOR MC9S12XEP100

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12XEP100CAL

Manufacturer:

TOSHIBA

Quantity:

72

Company:

Part Number:

MC9S12XEP100CAL

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 774 of 1328

- Download datasheet (9Mb)

Chapter 21 Serial Peripheral Interface (S12SPIV5)

21.3.2.5

Read: Anytime; read data only valid when SPIF is set

Write: Anytime

774

Module Base +0x0004

Module Base +0x0005

Because of an order from the United States International Trade Commission, BGA-packaged product lines and partnumbers

Reset

Reset

indicated here currently are not available from Freescale for import or sale in the United States prior to September 2010

W

W

R

R

The SPI data register is both the input and output register for SPI data. A write to this register

allows data to be queued and transmitted. For an SPI configured as a master, queued data is

transmitted immediately after the previous transmission has completed. The SPI transmitter empty

flag SPTEF in the SPISR register indicates when the SPI data register is ready to accept new data.

Received data in the SPIDR is valid when SPIF is set.

If SPIF is cleared and data has been received, the received data is transferred from the receive shift

register to the SPIDR and SPIF is set.

If SPIF is set and not serviced, and a second data value has been received, the second received data

is kept as valid data in the receive shift register until the start of another transmission. The data in

the SPIDR does not change.

If SPIF is set and valid data is in the receive shift register, and SPIF is serviced before the start of

a third transmission, the data in the receive shift register is transferred into the SPIDR and SPIF

remains set (see

If SPIF is set and valid data is in the receive shift register, and SPIF is serviced after the start of a

third transmission, the data in the receive shift register has become invalid and is not transferred

into the SPIDR (see

R15

T15

R7

T7

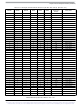

SPI Data Register (SPIDR = SPIDRH:SPIDRL)

0

0

7

7

Figure

R14

T14

R6

T6

0

0

6

6

Figure

Figure 21-7. SPI Data Register High (SPIDRH)

Figure 21-8. SPI Data Register Low (SPIDRL)

21-9).

MC9S12XE-Family Reference Manual , Rev. 1.23

21-10).

R13

T13

R5

T5

5

0

5

0

R12

T12

R4

T4

0

0

4

4

R11

T11

R3

T3

0

0

3

3

R10

T10

R2

T2

2

0

2

0

Freescale Semiconductor

R9

R1

T9

T1

0

0

1

1

R8

T8

R0

T0

0

0

0

0

Related parts for MC9S12XEP100CAL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: