D6417729RHF200BV Renesas Electronics America, D6417729RHF200BV Datasheet - Page 267

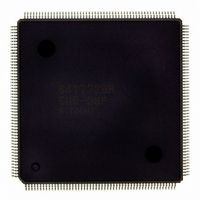

D6417729RHF200BV

Manufacturer Part Number

D6417729RHF200BV

Description

IC SUPER H MPU ROMLESS 208QFP

Manufacturer

Renesas Electronics America

Series

SuperH® SH7700r

Datasheet

1.D6417729RF133BV.pdf

(857 pages)

Specifications of D6417729RHF200BV

Core Processor

SH-3 DSP

Core Size

32-Bit

Speed

200MHz

Connectivity

EBI/EMI, FIFO, IrDA, SCI, SmartCard

Peripherals

DMA, POR, WDT

Number Of I /o

96

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.85 V ~ 2.15 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

208-QFP Exposed Pad, 208-eQFP, 208-HQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

D6417729RHF200BV

Manufacturer:

EVERLIGHT

Quantity:

1 000

Company:

Part Number:

D6417729RHF200BV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 267 of 857

- Download datasheet (5Mb)

Table 8.3

Branch

Delay

No delay

3. The location indicated by IA, the address prior to the branch, depends on the type of branch.

4. BRSR, BRDR, and BRFR have a four-queue structure. When reading addresses stored in a PC

If PID is an odd number, the value incremented by 2 indicates the instruction buffer, but the

equations in the table do not take this into account. Therefore, the calculation can be performed

using the values of BSA stored in BRSR and PID stored in BRFR.

a. Branch instruction: Branch instruction address

b. Repeat loop: Second-before-last instruction of the repeat loop

c. Interrupt: Instruction executed immediately before the interrupt

In a repeat loop consisting of no more than three instructions, an instruction fetch cycle is not

generated. A PC trace is invalid, since the branch destination address is unknown.

trace, reads are performed from the head of the queue. BRFR, BRSR, and BRDR are read in

that order. After BRDR is read, the queue shifts by one. BRSR and BRDR should be read by

longword access. Also, the PC trace has a trace pointer, which initially points to the bottom of

the queues. The first pair of branch addresses will be stored at the bottom of the queues, then

push up when next pairs come into the queues. The trace pointer will points to the next branch

address to be executed, unless it got push out of the queues. When the branch address has been

executed, the trace pointer will shift down to next pair of addresses, until it reaches the bottom

of the queues. After switching the PCTE bit (in BRCR) off and on, the values in the queues are

invalid. The read pointer stay at the position before PCTE is switched, but the trace pointer

restart at the bottom of the queues.

Repeat_Start: inst (1)

Repeat End:

The start address of the interrupt routine is stored in BRDR.

BSA Values Stored in Exception Handling before Execution of Branch

Destination Instruction

Branch Destination

(Dest)

4n

4n + 2

4n or 4n + 2

inst (n)

inst (2)

inst (n–1) ;----->Address calculated from BRSR and BRFR

:

BSA

4n

4n + 2

4n

;

;----->BRDR

;

Branch Source Address Calculable

by Means of BRSR and BRFR

Exec = IA = BSA – 2

Dest = BSA

Exec = IA = BSA – 2

Rev. 5.0, 09/03, page 219 of 806

PID

PID

Related parts for D6417729RHF200BV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: