D6417729RHF200BV Renesas Electronics America, D6417729RHF200BV Datasheet - Page 410

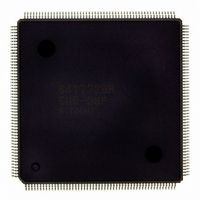

D6417729RHF200BV

Manufacturer Part Number

D6417729RHF200BV

Description

IC SUPER H MPU ROMLESS 208QFP

Manufacturer

Renesas Electronics America

Series

SuperH® SH7700r

Datasheet

1.D6417729RF133BV.pdf

(857 pages)

Specifications of D6417729RHF200BV

Core Processor

SH-3 DSP

Core Size

32-Bit

Speed

200MHz

Connectivity

EBI/EMI, FIFO, IrDA, SCI, SmartCard

Peripherals

DMA, POR, WDT

Number Of I /o

96

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.85 V ~ 2.15 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

208-QFP Exposed Pad, 208-eQFP, 208-HQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

D6417729RHF200BV

Manufacturer:

EVERLIGHT

Quantity:

1 000

Company:

Part Number:

D6417729RHF200BV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 410 of 857

- Download datasheet (5Mb)

11.3.7

Waits between Access Cycles

A problem associated with higher external memory bus operating frequencies is that data buffer

turn-off on completion of a read from a low-speed device may be too slow, causing a collision

with data in the next access. This results in lower reliability or incorrect operation. To avoid this

problem, a data collision prevention feature has been provided. This memorizes the preceding

access area and the kind of read/write. If there is a possibility of a bus collision when the next

access is started, a wait cycle is inserted before the access cycle thus preventing a data collision.

There are two cases in which a wait cycle is inserted: when an access is followed by an access to a

different area, and when a read access is followed by a write access from the SH7729R. When the

SH7729R performs consecutive write cycles, the data transfer direction is fixed (from the

SH7729R to other memory) and there is no problem. With read accesses to the same area, in

principle, data is output from the same data buffer, and wait cycle insertion is not performed. Bits

AnIW1 and AnIW0 (n = 0, 2–6) in WCR1 specify the number of idle cycles to be inserted

between access cycles when a physical space area access is followed by an access to another area,

or when the SH7729R performs a write access after a read access to physical space area n. If there

is originally space between accesses, the number of idle cycles inserted is the specified number of

idle cycles minus the number of empty cycles.

Waits are not inserted between accesses when bus arbitration is performed, since empty cycles are

inserted for arbitration purposes.

Rev. 5.0, 09/03, page 362 of 806

Related parts for D6417729RHF200BV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: